# A novel approach to radiation detector readout system for space borne instrumentation

A Thesis submitted by

## **Arpit Patel**

(Enrolment No. 17PH21)

For the partial fulfillment of the award of the degree of

## Doctor of philosophy (Ph.D.)

Under the guidance of

### Prof. Himanshu S Mazumdar

Professor E.C and Head R&D Center Faculty of Technology, Dharmsinh Desai University (DDU)

Department of Electronics & Communication Engineering Faculty of technology

Dharamsinh Desai University, Nadiad, Gujarat.

August-2022

**CERTIFICATE**

This is to certify that the content of this thesis titled "A novel approach to

radiation detector readout system for space borne instrumentation" is the original work

of Mr. Arpit Patel (17PH21) carried out under my supervision. I further certify with

best of my knowledge that the work has not been submitted either partly or fully to any

other university or body - in quest of a degree, diploma and/or any other kind of

academic award.

Dr. Himanshu S. Mazumdar

Research Guide

Professor, E. C and Head R & D Center,

D. D. University

Nadiad- 387001

Date:

Place: Nadiad

i

## **CANDIDATE'S DECLARATION**

The work described in this thesis entitled "A novel approach to radiation detector readout system for space borne instrumentation" is carried out solely by me under the guidance of Prof. Himanshu Mazumdar, except for those colleagues and other workers referred/acknowledged in the text. I hereby declare that no part of this thesis has been previously submitted to this or any other university as part of the requirement for a higher degree.

| Arpit Patel | Date:       |

|-------------|-------------|

| (17DH21)    | Dl M. 4'. 4 |

(17PH21) Place: Nadiad

## **DEDICATION**

To my caring Mother & Father,

loving wife & cute daughter

and

To all my well wishers

#### **ACKNOWLEDGEMENTS**

Words fail us to express my gratitude to my guide, **Prof. Himanshu Mazumdar**. I owe my deep sense of appreciation to him for his constant vigilance with the right amount of freedom, not only as a guide but as a guardian too. His efforts and encouragement will never be forgotten.

I am highly grateful to Dr. Y B Acharya for his invaluable advice and continuous support. His immense knowledge and great experience have encouraged me throughout my academic research and daily life.

I would like to thank the Director and Dean, PRL for allowing me to carry out my research and also helping me in providing the required resources for the research. I also would like to thank Prof. Santosh Vadawale, Dr. M. Shanmugam, and Prof. Varun Sheel for their support and encouragement.

I would like to thank Mr. N P S Mithun for his help in simulations and Mr. Tinkal Ladiya for his help in the fabrication and testing of electronics designs.

I am pleased to thank the vice chancellor of DDU for giving me this opportunity to carry out my research at DDU. I like to thank the Dean, Registrar, HOD of ECE, HOD of IC, HOD of CE, and DDU for their support and guidance.

I would like to thank Prof. Hardip Shah and Mr. Marmik Soni for their guidance in the Advance digital signal processing (ADSP) coursework. Mr. Himanshu Purohit, Mr. Satvik Patel, and Shri. Vitul Patel are thanked for their support.

At last, I would like to thank all the Planetary Science Division (PSDN) and Physical Research Laboratory (PRL) colleagues who have directly or indirectly helped me in my research activity.

#### **ABSTRACT**

This thesis focuses on the new signal readout technique from the radiation detector which can be used for future space missions ensuring to have better in terms of resolution, mass, and power compared to available signal readout techniques. In radiation detector signal processing usually, the charge-sensitive pre-amplifier converts the small charge signal coming from the semiconductor-based detector into voltage form and then the signal is further amplified to measure the energy of the incoming radiation. The voltage pulse from a charge-sensitive pre-amplifier (CSPA) is amplified with the use of a shaping amplifier which reduces the signal bandwidth. To have better energy resolution, precise measurement of the peak amplitude of shaping amplifier output is required. For multiple detector systems, currently available peak height analysis (PHA) methods are quite power consuming and difficult to implement in Field Programmable Gate Arrays (FPGA). In this direction, the research is carried out and a technique is developed that uses low sampling analog to digital converter and interpolation technique to precisely measure the peak of the analog pulse. The main topics of interest are, the development of a novel signal readout technique using the interpolation method, the selection of appropriate interpolation technique and performance comparison with existing readout techniques. The silicon drift detector (SDD) based soft X-ray spectrometer instrument is developed and used to compare the PHA techniques. Chapter 1 gives a brief objective of the research goal, and chapter 2 includes the literature review and background of various radiation detectors and their readout techniques. Chapter 3 discuss the design details of various pulse height analysis methods. The methods are implemented on hardware and various parameters are obtained to compare with the proposed method. Chapter 4 discusses the implementation of a new method with the use of the interpolation technique and contains results for the proposed method and a comparison with other methods. The energy resolution is considered the main performance criteria. To select the most suitable interpolation method for the proposed method, various interpolation methods are compared by implementing them on hardware. Chapter 5 gives a summary of the research work and future plans.

## TABLE OF CONTENTS

| L |     |                                        |     |

|---|-----|----------------------------------------|-----|

| C | ERT | TIFICATE                               | i   |

| C | ANI | DIDATE'S DECLARATION                   | ii  |

| D | EDI | CATION                                 | iii |

| A | CKN | NOWLEDGEMENTS                          | iv  |

| A | BST | RACT                                   | v   |

| T | ABL | LE OF CONTENTS                         | vi  |

| L | IST | OF FIGURES                             | ix  |

| L | IST | OF TABLES                              | xiv |

| L | IST | OF ABBREVIATIONS                       | xv  |

| 1 | IN  | TRODUCTION                             | 1   |

|   | 1.1 | Research objectives and result         | 2   |

|   | 1.2 | Plan of thesis chapters                | 3   |

| 2 | TI  | HEORETICAL BACKGROUND                  | 5   |

|   | 2.1 | Types of radiation relevant to space   | 5   |

|   | 2   | .1.1 Non-ionizing radiation            | 5   |

|   | 2   | .1.2 Ionizing radiation                | 6   |

|   | 2.2 | Systems used for radiation measurement | 8   |

|   | 2.3 | Summary                                | 12  |

| 3 | E   | XPERIMENTAL METHODS                    | 13  |

|   | 3.1 | Detector and Pre-amplifier             | 13  |

|   | 3   | .1.1 Silicon Drift Detector (SDD)      | 13  |

|   |     | 3.1.1.1 Working principle of SDD       | 14  |

|   | 3.1.1   | .2 SDD for X-ray measurements                        | 16   |

|---|---------|------------------------------------------------------|------|

|   | 3.1.1   | .3 SDDs in space missions                            | 18   |

|   | 3.1.1   | .4 SDD detector module used for an experiment        | 18   |

|   | 3.1.1   | .5 Design of Charge Sensitive Pre-Amplifier (CSPA):  | 21   |

|   | 3.1.2   | Shaping Amplifier                                    | 23   |

|   | 3.1.3   | High Voltage Bias Generation for SDD                 | 26   |

|   | 3.2 Pu  | lse height measurement techniques                    | - 28 |

|   | 3.2.1   | The conventional peak detection technique            | 29   |

|   | 3.2.1   | .1 Peak hold detector                                | 29   |

|   | 3.2.1   | .2 Analog to digital converter (ADC)                 | 30   |

|   | 3.2.1   | .3 Experimental setup and result                     | 31   |

|   | 3.2.2   | Real-time pulse shaping via digital pulse processing | 32   |

|   | 3.2.3   | Linear Discharge technique                           | 38   |

|   | 3.2.4   | Pulse width modulation (PWM) technique               | 41   |

|   | 3.3 Su  | mmary                                                | - 43 |

| 4 | IMPL    | EMENTATION AND RESULTS OF THE PROPOSED               | ١    |

|   | PULS    | E HEIGHT ANALYSIS METHOD                             | - 45 |

|   | 4.1 Pro | oposed pulse height analysis method                  | - 45 |

|   | 4.2 Int | erpolation methods                                   | - 47 |

|   | 4.2.1   | Nearest neighbor Interpolation                       | 47   |

|   | 4.2.2   | Linear Interpolations                                | 48   |

|   | 4.2.3   | Lagrange's interpolation                             | 49   |

|   | 4.2.4   | Newton Raphson Interpolation                         | 50   |

|   | 4.2.5   | Cubic interpolation                                  | 50   |

|   | 4.2.6   | Whittaker–Shannon interpolation                      | 51   |

|   | 4.2.7   | Neville's Algorithm for interpolation                | 52   |

| 4.3  | Implementation of interpolation methods                     | 52 |

|------|-------------------------------------------------------------|----|

| 4    | .3.1 FPGA Implementation                                    | 53 |

| 4    | .3.2 Experimental Setup & Validation                        | 53 |

| 4.4  | Experiment to derive optimum interpolation points           | 60 |

| 4.5  | Experiment to derive required shaping time                  | 62 |

| 4.6  | The proposed algorithm's performance with the silicon drift |    |

|      | detector (SDD) configuration                                | 67 |

| 4.7  | Summary                                                     | 73 |

| 5 SU | JMMARY AND FUTURE PLAN                                      | 74 |

| 5.1  | Summary of the research work                                | 74 |

| 5.2  | Future plan                                                 | 75 |

| REFE | CRENCES                                                     | 76 |

| PUBL | ICATIONS                                                    | 85 |

## LIST OF FIGURES

| Figure 2.1: Types of radiation on the electromagnetic spectrum [2]                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.2: Types of decay for various radiation [3]                                                                                                                                                                                |

| Figure 2.3: Schematic representation of the production of charge carriers in direct and indirect conversion type X-ray detectors [8]                                                                                                |

| Figure 2.4: Classification of radiation detectors                                                                                                                                                                                   |

| Figure 2.5: Radiation detector readout block schematic                                                                                                                                                                              |

| Figure 3.1: Schematic representation of sideward depletion concept [64]                                                                                                                                                             |

| Figure 3.2: Schematic representation of the working principle of silicon microstrip detector [64]                                                                                                                                   |

| Figure 3.3: The electron guiding potential distribution in the drift region of the SDD pointing towards the anode [64]                                                                                                              |

| Figure 3.4: Schematic representation of a circular SDD with anode at the center (courtesy: KETEK, GmbH) [77]                                                                                                                        |

| Figure 3.5: The possible electron path (field line) inside the SDD with 300-micron thickness [77].                                                                                                                                  |

| Figure 3.6: Quantum efficiency of 450 and 900-micron thick SDDs with thin dead layer [78].                                                                                                                                          |

| Figure 3.7: Silicon drift detector (SDD) module with lid, KETEK VITUS H80 (left).  Views of the TEC and on-chip collimator from an unencapsulated silicon drift detector (SDD) module (right). [24] (Image courtesy of KETEK GmbH.) |

| Figure 3.8: SDD module schematic view [85] (courtesy: KETEK, GmbH - H80) 19                                                                                                                                                         |

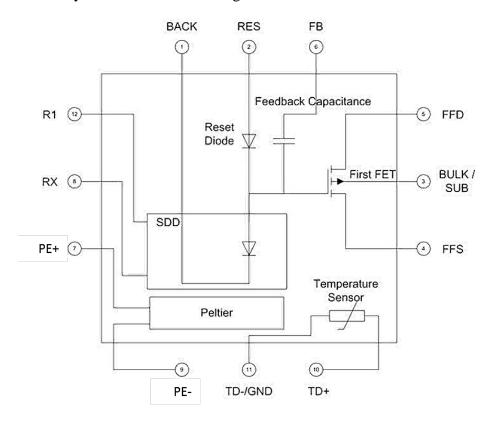

| Figure 3.9: Internal electrical interconnection diagram of SDD module [86] (courtesy: KETEK, GmbH).                                                                                                                                 |

| Figure 3.16: Block schematic of pulse reset type Charge Sensitive Pre-Amplifier (CSPA) design [105]                                                                                                                                 |

| Figure 3.17: | CRO screenshot for ramp signal output from CSPA (left), Step on the                                                                                                                                                                                                                                    |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | ramp signal indicating X-ray interaction with the SDD detector (right).                                                                                                                                                                                                                                |

|              |                                                                                                                                                                                                                                                                                                        |

| Figure 3.18: | Simulated shaping amplifier output for equal CR-RC time constants 25                                                                                                                                                                                                                                   |

| Figure 3.19: | Simulated shaping amplifier output with one CR and multiple RC stages.                                                                                                                                                                                                                                 |

| Figure 3.20: | Block schematic of CR-(RC) <sup>2</sup> type shaping amplifier                                                                                                                                                                                                                                         |

| Figure 3.21: | Schematic representation of SDD with HV bias filtering requirement (courtesy: KETEK GmbH)                                                                                                                                                                                                              |

| Figure 3.22: | The block schematic of the high voltage generation circuit                                                                                                                                                                                                                                             |

| Figure 3.24: | Block diagram of the peak detector-based spectrometer's front-end and back-end circuits                                                                                                                                                                                                                |

| Figure 3.25: | AMPTEK make PH300 Hybrid peak detector module(left), Peak detector operational timing diagram for peak hold and discharge (right) [47] 30                                                                                                                                                              |

| Figure 3.26  | : X-ray spectrometer set up utilizing peak detector-based processing circuitry and a front end compatible with silicon drift detectors (SDDs).                                                                                                                                                         |

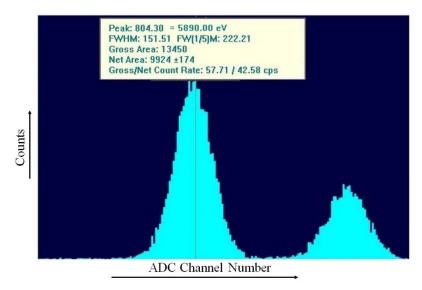

| Figure 3.27: | Operation signals for a peak hold detector in operation (top), spectra from a <sup>55</sup> Fe source produced using a traditional peak detection method. (bottom)                                                                                                                                     |

| Figure 3.28: | Block diagram of the digital pulse processing                                                                                                                                                                                                                                                          |

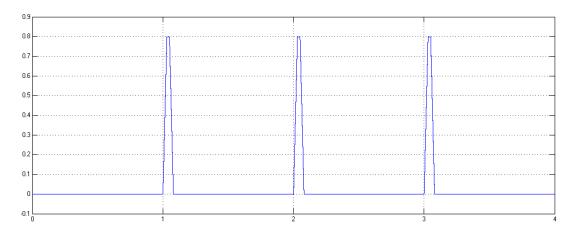

| Figure 3.29: | Fast ADC is used to digitize the input signal from the CSPA (blue), and samples are then saved in internal memory of the FPGA. (top), Red represents the output of a trapezoidal wave with a flat top. The height of the output pulse is inversely proportional to the height of the input pulse [103] |

| Figure 3.30: | Digital trapezoidal shaper block diagram. [104]                                                                                                                                                                                                                                                        |

| Figure 3.31: | The MATLAB simulation results for the digital trapezoidal shaper 36                                                                                                                                                                                                                                    |

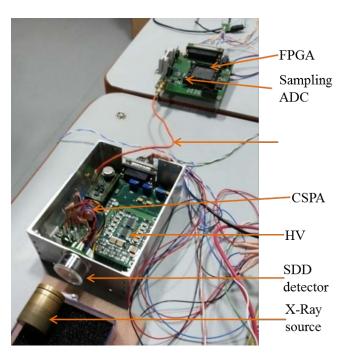

| Figure 3.32:  | FPGA board with digital pulse processing interfaced with setup for SDD                                                                                                                                                                                           |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | detector front-end                                                                                                                                                                                                                                               |

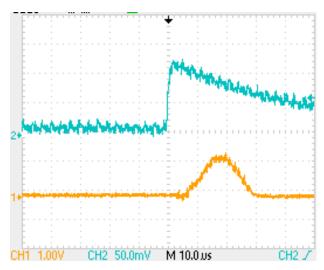

| Figure 3.33:  | CRO screenshot for CSPA output (blue) and Trapezoidal filter output through DAC (orange)                                                                                                                                                                         |

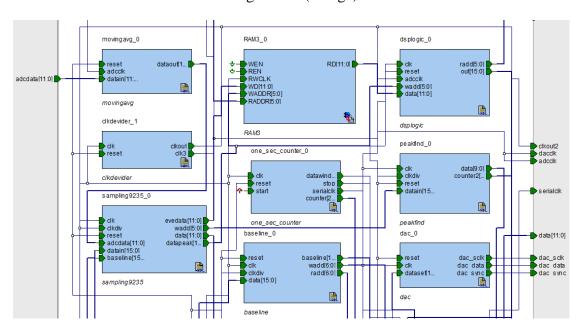

| Figure 3.34:  | FPGA implementation for digital pulse processing using libero smart design tool (For Microsemi make FPGAs)                                                                                                                                                       |

| Figure 3.35:  | The <sup>55</sup> Fe spectral data was collected utilizing the digital pulse processing method of the ORTEK MCA                                                                                                                                                  |

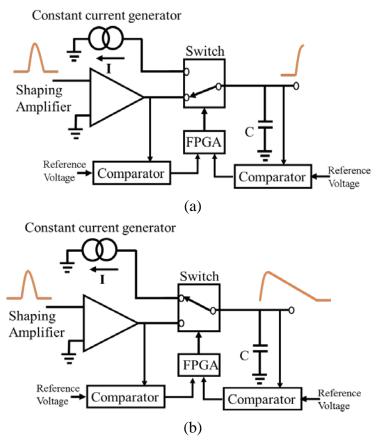

| Figure 3.36:  | Peak detection and linear discharge circuit concept. (a) Capacitor (C) is in charging mode with analog input signal coming from shaping amplifier. (b) Capacitor (C) in discharge mode with constant current path (bottom).                                      |

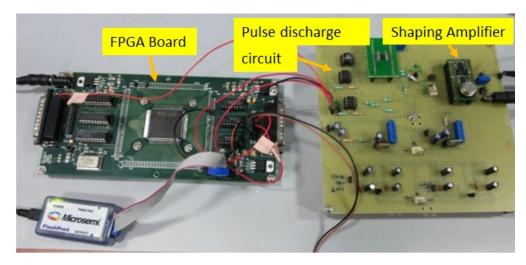

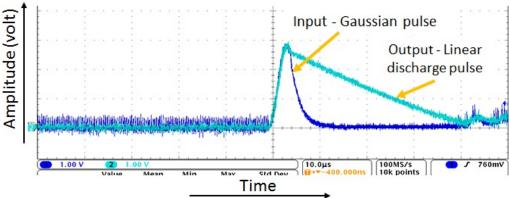

| Figure 3.37:  | Hardware setup for a pulse linear discharge circuit (top), oscilloscope waveform displaying the output of a shaping amplifier (dark blue) and a linear discharge pulse (light blue). The Y-axis has a 1 V grid size, whereas the X-axis has a 10 s grid (bottom) |

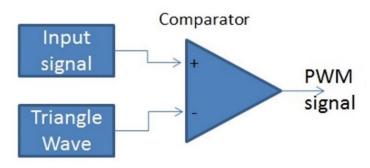

| Figure 3.38:  | Pulse width modulation basic concept                                                                                                                                                                                                                             |

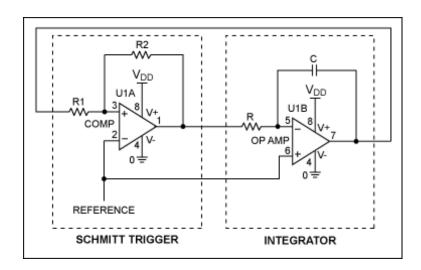

| Figure 3.39:  | Design concept for a basic triangular-wave generator [107]                                                                                                                                                                                                       |

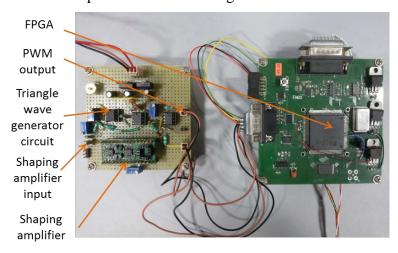

| Figure 3.40:  | PWM hardware and FPGA interface                                                                                                                                                                                                                                  |

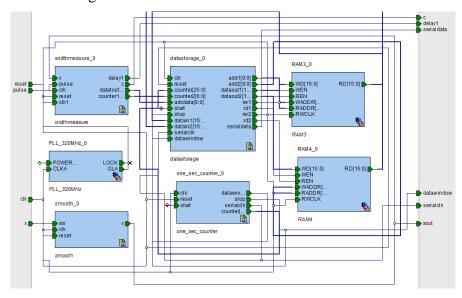

| Figure 3.41:  | FPGA implementation of PWM algorithm, data storage and transfer using Libero smart design flow. 42                                                                                                                                                               |

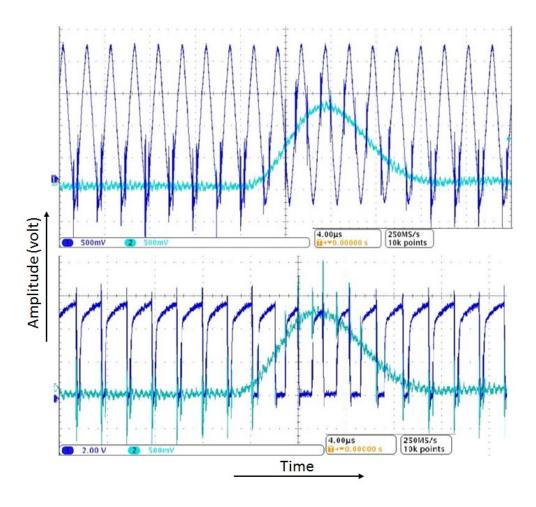

| Figure 3.42:  | Triangle signal compared with input semi-gaussian pulse (top), PWM output with semi-gaussian input pulse (bottom)                                                                                                                                                |

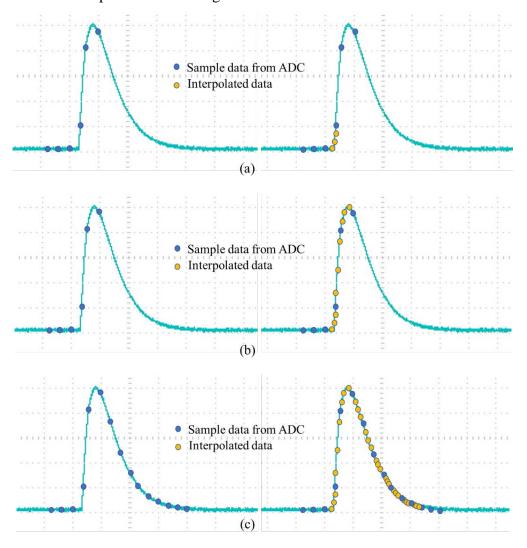

| Figure 4.1:   | Illustration of the suggested interpolation method using a semi-gaussian pulse sampled at a low sampling rate (left part of a, b, c). after sample data interpolation (right part of a, b, c)                                                                    |

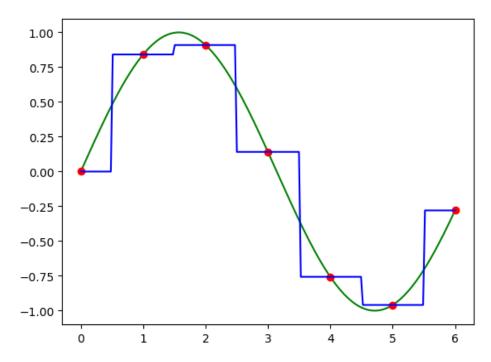

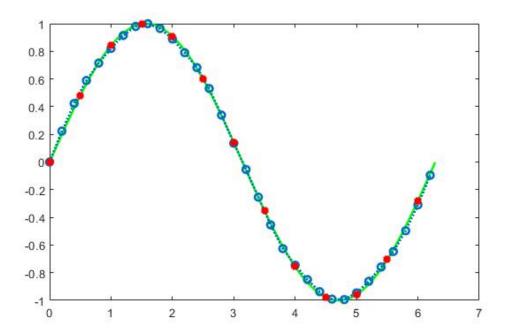

| Figure 4.2: 7 | The continuous function $f(x) = \sin(x)$ in green, the sampled function in red and the nearest interpolated function in blue                                                                                                                                     |

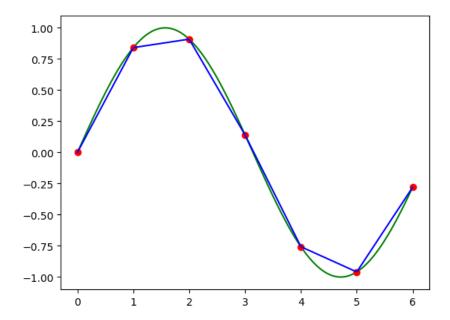

| Figure 4.3: T | The continuous function $f(x) = \sin(x)$ in green, the sampled function in red, and the linear interpolated function in blue                                                                                                                                     |

| Figure 4.4: The continuous function $f(x) = \sin(x)$ in green, the sampled function in red,                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| and the Lagrange's interpolated function in blue doted50                                                                                                                                                                                 |

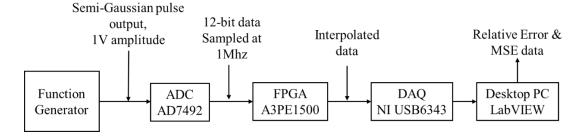

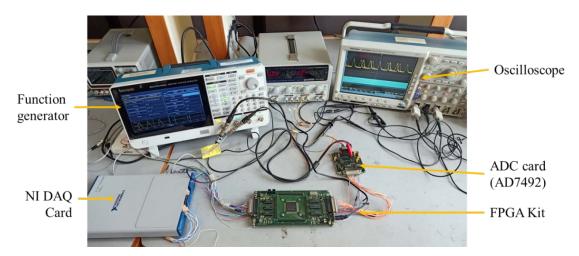

| Figure 4.5: Experimental scheme for Relative error (RE) measurement                                                                                                                                                                      |

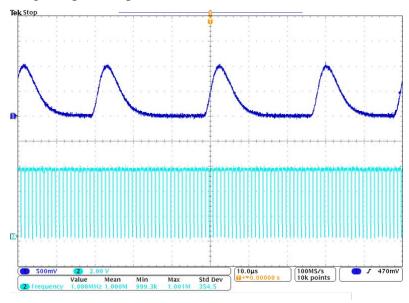

| Figure 4.6: Waveform obtained using an oscilloscope showing semi-gaussian pulse from function generator output (dark blue) and convert start pulse for ADC from FPGA (light blue).                                                       |

| Figure 4.7: Experimental setup for Relative error (RE) measurement                                                                                                                                                                       |

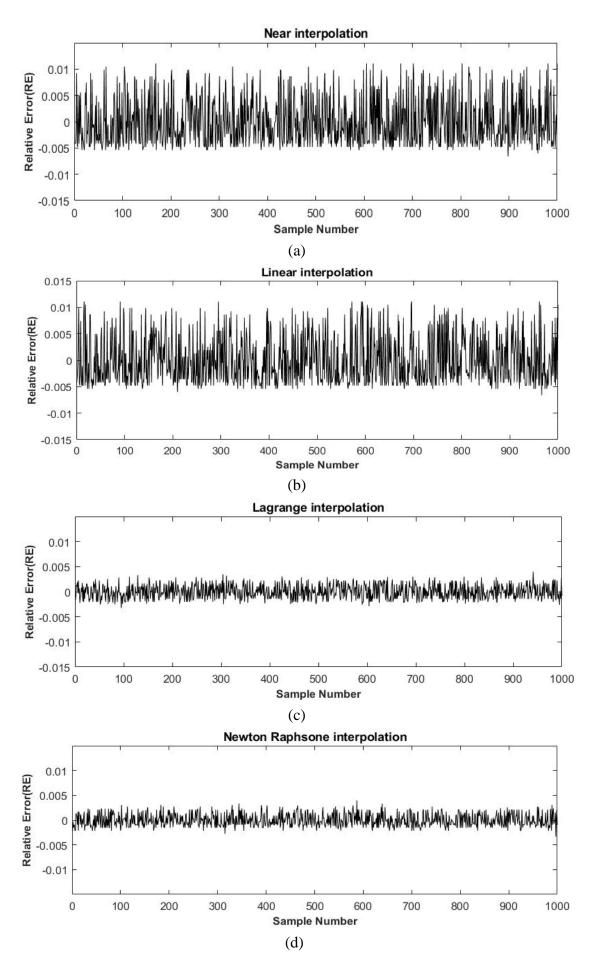

| Figure 4.8: Relative error (RE) values for different interpolation methods for 1000 sample data                                                                                                                                          |

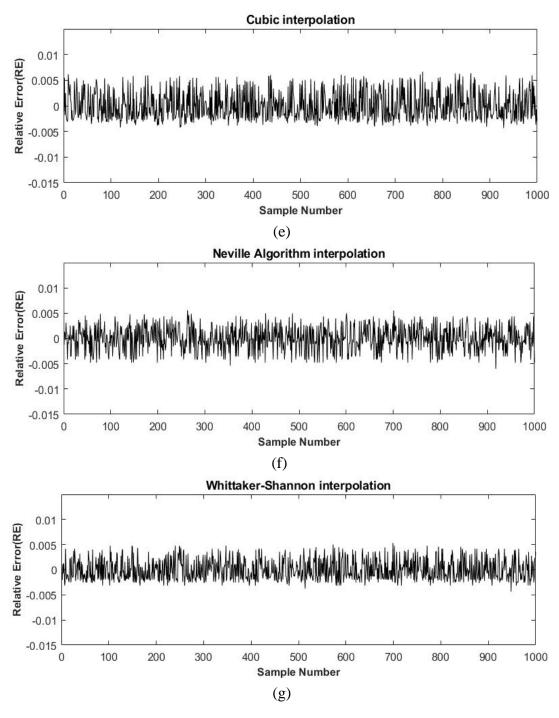

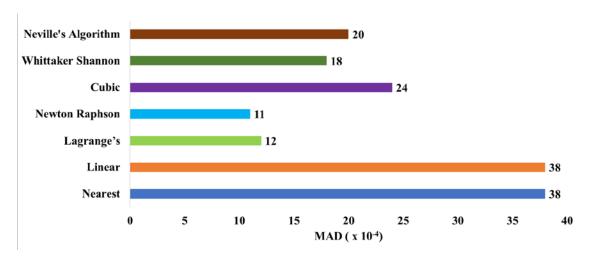

| Figure 4.9: Mean square error (MSE) values for different interpolation methods for 1000 sample data                                                                                                                                      |

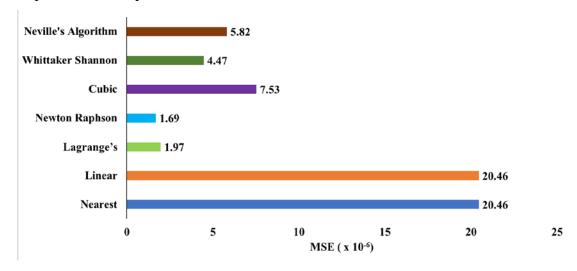

| Figure 4.10: Mean absolute deviation (MAD) values for different interpolation methods for 1000 sample data                                                                                                                               |

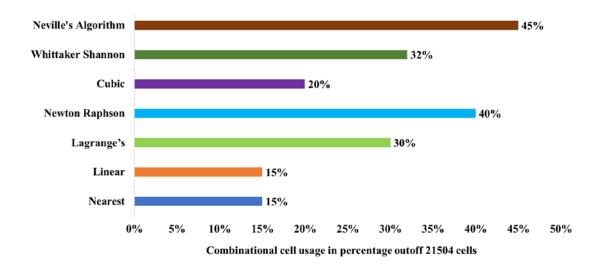

| Figure 4.11: Combinational cell utilization of A3PE1500 FPGA for different interpolation methods                                                                                                                                         |

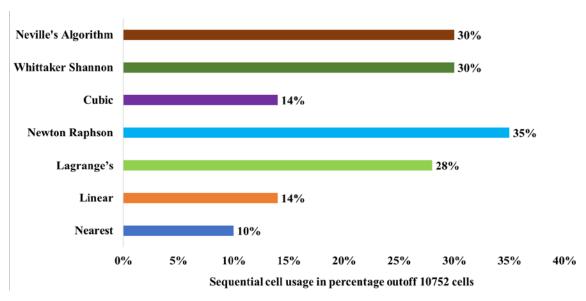

| Figure 4.12: Sequential cell utilization of A3PE1500 FPGA for different interpolation methods                                                                                                                                            |

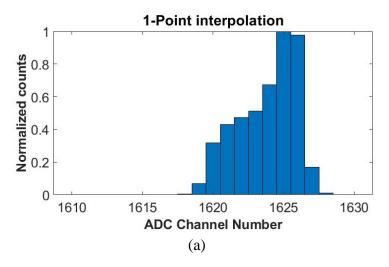

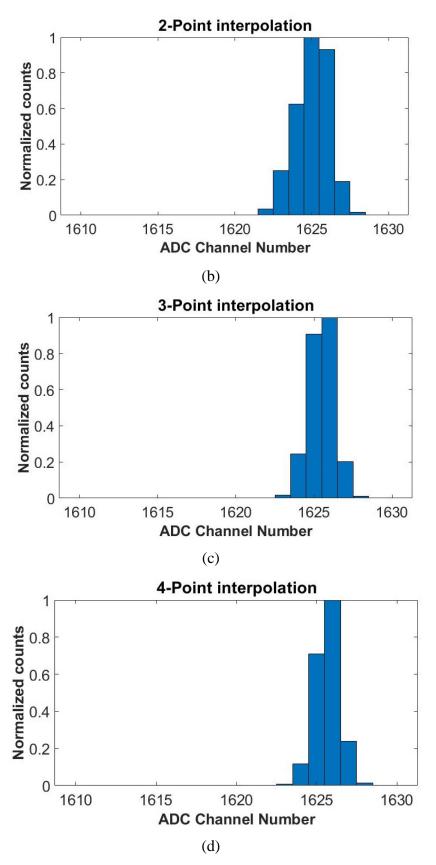

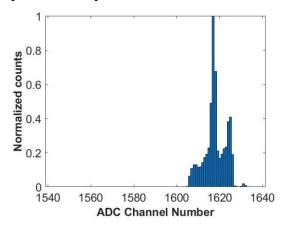

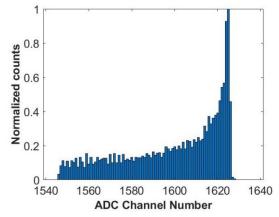

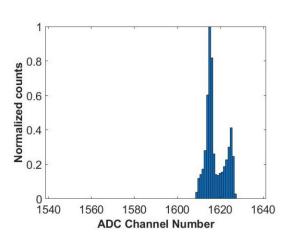

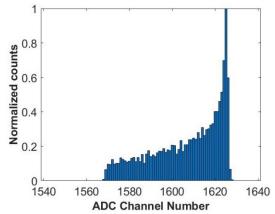

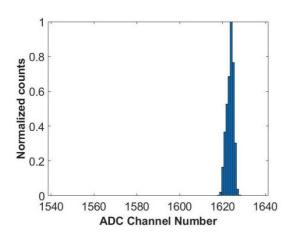

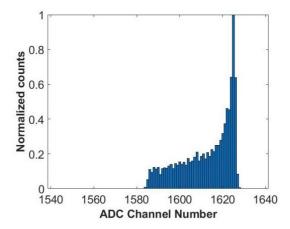

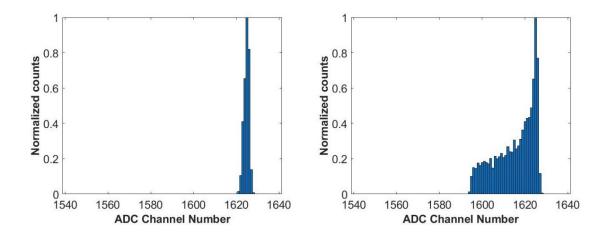

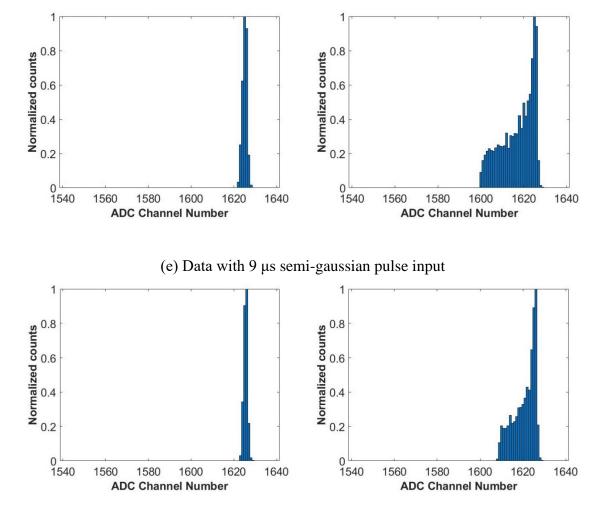

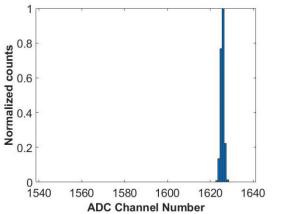

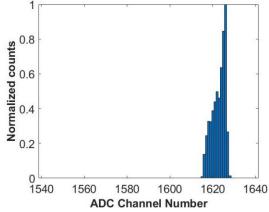

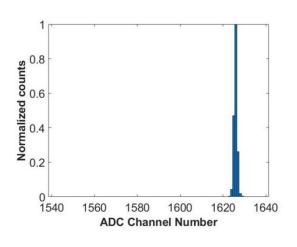

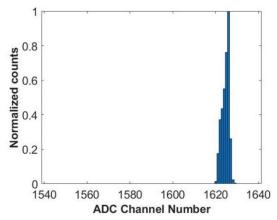

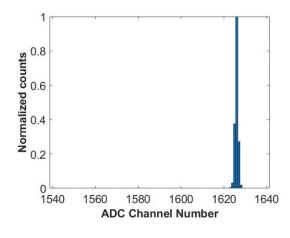

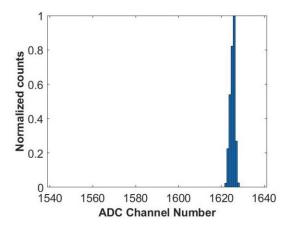

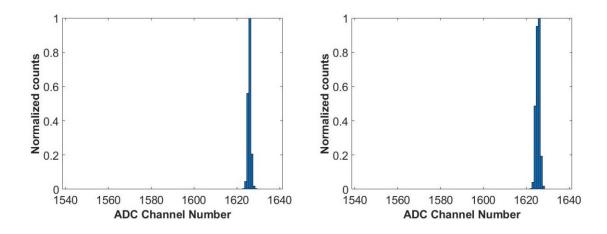

| Figure 4.13: Plots of the spectrum for various interpolation points between two raw data points. (a) One-point interpolation, (b) two-point interpolation, (c) three-point interpolation, and (d) four-point interpolation are examples. |

| Figure 4.14: Peak height histograms constructed using interpolated data (left) and raw sample data (right)                                                                                                                               |

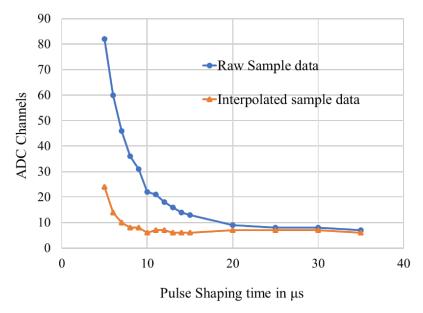

| Figure 4.15: Plot of variance (spectral dispersion) in ADC channels vs signal shaping time                                                                                                                                               |

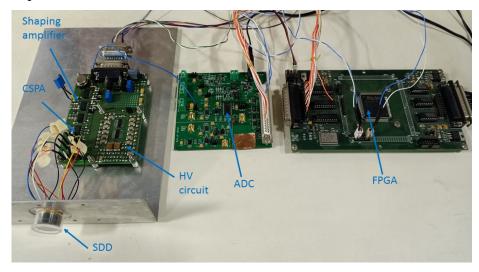

| Figure 4.16: Front-end setup interface with ADC and FPGA cards for the Silicon Drift Detector (SDD)                                                                                                                                      |

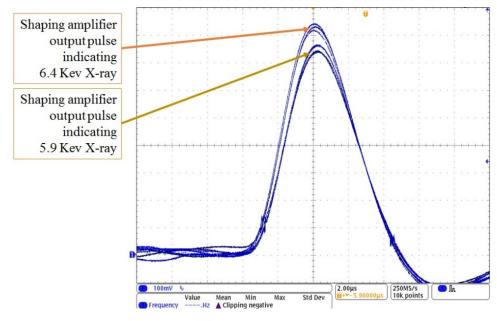

| Figure 4.17: CRO image shows the output of the shaping amplifier. The Y-axis has a 100-mV grid size, whereas the X-axis has a 2 µs grid                                                                                                  |

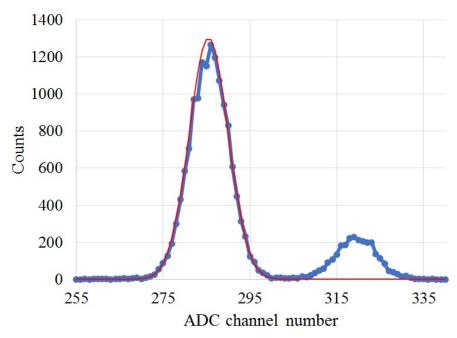

| Figure 4.18: | Spectral data were collected by illuminating a <sup>55</sup> Fe X-ray source with a                          |

|--------------|--------------------------------------------------------------------------------------------------------------|

|              | real-time interpolation approach that was developed on an FPGA. A                                            |

|              | fitting with gaussian function using red line is over-plot to the main peak.                                 |

|              |                                                                                                              |

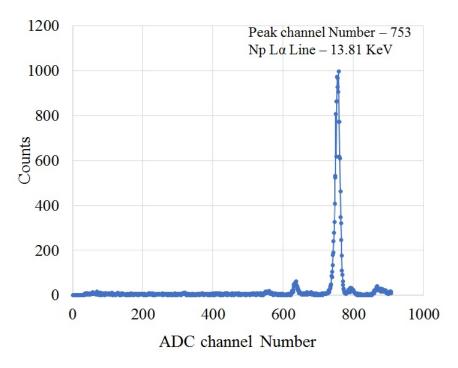

| Figure 4.19: | Spectral data collected by illuminating <sup>241</sup> Am X-ray source (Real-time interpolation method used) |

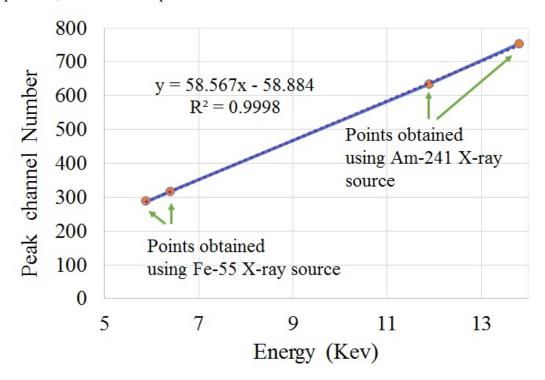

| Figure 4.20: | Plot of the incident energetic lines' peak channel as a function of energy.                                  |

|              | The residuals are displayed together with an over-plotted dashed trend                                       |

|              | line on the data70                                                                                           |

## LIST OF TABLES

| Table 3.1: Specifications of the SDD module planned for the experiment               |

|--------------------------------------------------------------------------------------|

| Table 3.2: SDD HV bias voltage, current and filtering on each HV line                |

| Table 4.1: Comparison of various pulse processing techniques for energy resolution   |

| Peaking time, Event process time, and Power71                                        |

| Table 4.2: Comparison of various pulse processing techniques for pile-up event, FPGA |

| processing requirement, Mass, and PCB area requirement                               |

#### LIST OF ABBREVIATIONS

Abbreviation Full form

ADC Analog to Digital Converter

ALICE A Large Ion Collider Experiment

AM Amplitude Modulation

ASIC Application Specific Integrated Circuit

BGO Bismuth Germanate

CCE Charge Collection Efficiency

CdTe Cadmium Telluride

CdZnTe Cadmium Zinc Telluride

CME Coronal Mass Ejections

CRO Cathode ray oscilloscope

Csl (Tl) Cesium Iodide (Thallium)

CSPA Charge Sensitive Pre-Amplifier

DAC Digital to Analog converter

DSSD Double Sided Silicon strip Detector

DPP Digital Pulse Processing

E Incident Photon Energy

ELF Extremely Low Frequency

ESA European Space Agency

eV electron Volts

FEE Front-End Electronics

FM Frequency Modulation

FPGA Field Programmable Gate Array

FWHM Full Width Half Maximum

Ge Germanium

GCR Galactic Cosmic Rays

GM Geiger-Muller

GRS Gamma Ray Spectrometer

KV Kilo Volts

KeV Kilo electron Volts

LaBr<sub>3</sub> Lanthanum Bromide (cerium)

LAD Large Area silicon Detectors

LN<sub>2</sub> Liquid Nitrogen

LOFT Large Observatory for X-ray Timing

MAD Mean Absolute error

MCA Multi-Channel Analyzer

MER Mars Exploration Rover

MOS Metal Oxide Semiconductor

MSE Mean square error

NaI (Tl) Sodium Iodide (Thallium)

PHA Pulse Height Analysis

PMT Photomultiplier Tube

PWM Pulse width modulation

RE Relative error

SDD Silicon Drift Detector

Si Silicon

Si (Li) Silicon Lithium

SPE Solar Particle Events

SiPM Silicon Photomultiplier

SSD Silicon Strip Detector

UV Ultra Violate

XRF X-Ray Fluorescence

Z Atomic Number

#### INTRODUCTION

Developing a space-borne instrument is a challenging task, as the instrument has to survive very hostile space environment. The cost of launch is determined by the payload's weight. In that regard, it is necessary to have the least amount of mass, power, and size instrument onboard in order to complete tasks with the best possible performance. Any instrument onboard a spacecraft is likely to be exposed to harsh radiation, extreme temperature swings, and high vacuum conditions. The instrument should also be able to withstand launch vehicle vibration. At various levels of the instrument design, such as selecting components/devices with space qualification, desired radiation testing, design, and packaging of the instrument, care must be taken for the above-mentioned aspects. Instruments built with Commercial-Off-The-Shelf (COTS) components will not withstand the harsh space environment and satellite launch loads. For these reasons, "space instruments are custom-designed one-of-a-kind instruments, and the construction of such a one-of-a-kind instrument is dependent on the mission and the instrument configuration required for the scientific application".

Radiation detectors are widely used for measuring radiation emitted by various space objects in the X-ray, Gamma-ray, or high-energy particle regions of the spectrum. Ionizing and non-ionizing radiation are the two main types of radiation. Non-ionizing radiation from ultraviolet is less energetic. The atoms and molecules that interact with UV light particles receive energy from them but do remove their electrons. There are several types of ionizing radiation, including galactic cosmic radiation, trapped radiation, and solar energetic particles. The Galactic cosmic radiation is emitted as massive clouds of high-energy charged particles believed to be emitted by supernovas. The earth's magnetic field is strong enough to catch the charge particles and, in the field, these particles travel in a spiral pattern. Solar particle events involve the Sun releasing energetic solar particles. Sudden, powerful storms may develop as a result of this.

Radiation detector instruments usually have a similar kind of readout method which contains CSPA, Shaping amplifier and pulse height analyzer. A suitable pulse

height analyzer is required based on instrument specifications such as energy resolution, count rate, mass, etc.

#### 1.1 Research objectives and result

Currently, astronomers are attempting to answer fundamental questions about the motion of matter orbiting close to a black hole's event horizon, the state of matter in neutron stars, and other solar studies. High-resolution Gamma-ray and X-ray timing will be used to achieve these scientific objectives, which entails monitoring X-ray photometric time series and energy spectra from a range of astrophysical compact objects (Galactic black holes, neutron stars, and extra-Galactic black holes in AGNs). For these tests, wide imaging capacity and superior spectral resolution are required. The Large Area Silicon Detectors (LAD) of size 108.5 mm x 70 mm, which uses the same technology and are based on the heritage of the detectors used in the Inner Tracking System of the ALICE experiment at the Large Hadron Collider at CERN, have recently been developed to measure the X-ray energy and timings [1]. In this experiment, the number of detector's anode readout required are 224 channels [1]. Similarly, there are many instruments where multi-channel readout is required to carry out measurements in different directions or to carry out large area readout.

There are currently no commercially available back-end electronics to read these many channels. The reading approaches that are currently available demand more mass, power, and processing. The development of a new pulse height analysis technique for spaceborne instruments is required in this direction. The technique should provide comparable or better performance while using less instrument mass, power, and size. The primary research goal is to create a novel pulse height measurement technique for radiation detector readout that performs similarly to existing PHA techniques. Because the technique employs interpolation, selecting the appropriate 1-D interpolation method is also an important goal.

It is demonstrated that the LaGrange's interpolation technique is best suited for the proposed method due to its low relative and mean square error. Lagrange's interpolation methods also consume fewer resources than other interpolation methods with comparable relative error and mean square error.

For the new method, the SDD based X-ray spectrometer is designed. The other known PHA methods are developed and compared with new designed method. The interpolation method gives 165 eV energy resolution at 5.9 keV by illumination <sup>55</sup>Fe

source in front of detector. The archived resolution may be enough for many of the radiation detector systems like Gamma-ray detector, particle detector or large area X-ray detector (which has many discrete X-ray detectors) etc.

#### 1.2 Plan of thesis chapters

The first chapter provides a brief overview of space instruments and the challenges involved in their development for use in space. Following that, the research objectives and short results of each activity are provided.

The second chapter discusses the various types of radiation and radiation detectors. In addition, the radiation detector technologies that have been developed over the last few years are being studied in terms of their working principle and possible readout techniques. The suitability of these detectors for the desired energy range is described by comparing their performances and highlighting their advantages and disadvantages.

The working principle of the Silicon drift detector based on the sideward depletion concept is discussed in Chapter 3. This chapter also discusses the concept and design details of the SDD-based X-ray spectrometer's subsystems. The CSPA concept, shaping amplifier, and HV bias are all thoroughly explained. The SDD-based X-ray spectrometer was built with commercially available qualified components and various backend electronics. The various pulse height analysis techniques were thoroughly discussed. To compare their performance, the techniques were developed and interfaced with the front-end electronics. The FWHM at 5.9 keV for each technique is calculated by illuminating the <sup>55</sup>Fe X-ray source in front of the detector.

The proposed methods and their implementation using an SDD detector and FPGA-based backend electronics are described in Chapter 4. This chapter also discusses the importance of researching various interpolation algorithms. The interpolation techniques were thoroughly examined and implemented on hardware in order to compare their performance in terms of relative error, mean square error, mean absolute deviation, and FPGA resource utilization. Based on the comparative study, the appropriate interpolation method was chosen to be implemented in the proposed method.

The results of the proposed method for pulse height analysis are obtained for various shaping time and interpolation points. The performance of <sup>55</sup>Fe and <sup>241</sup>Am X-

ray sources is also investigated. The proposed method's performance is assessed by measuring the FWHM, shaping time requirement, pile-up, and processing time.

Chapter 5 presents the research activity's conclusions as well as its future scope. We intend to expand our research into pileup correction for high-count rate applications. In addition, we are considering developing a hybrid / ASIC chip for the proposed method, which would incorporate a large number of readout channels with higher resolution in a small package.

#### 2 THEORETICAL BACKGROUND

In this chapter basic idea about radiation and its types are discussed. Various radiation detectors and their working principles are explained in detail. The methodology for various detector readouts are explained in detail.

#### 2.1 Types of radiation relevant to space

Before creating any instrument for radiation detection, it is necessary to understand the type of radiation. A type of energy called radiation is released or transferred as rays, electromagnetic waves, or particles. Some forms of radiation, like visible light and infrared radiation, may be seen or felt, while others, like X-rays and gamma-rays, are invisible and can only be viewed directly or indirectly with the use of special equipment. Non-ionizing radiation and ionizing radiation are the two main categories of radiation.

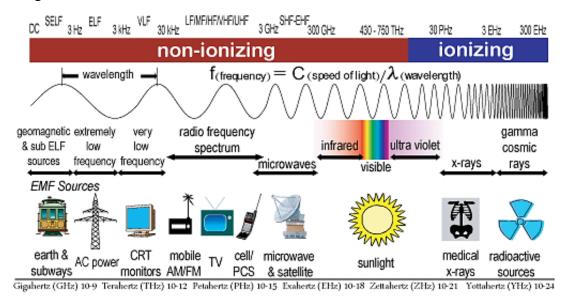

Figure 2.1: Types of radiation on the electromagnetic spectrum [2].

#### 2.1.1 Non-ionizing radiation

Non-ionizing radiation sources are used by and exposed to people every day. The energy contained in this type of radiation is insufficient to ionize atoms or molecules. Non-ionizing radiation is used by GPS units, microwave ovens, FM and AM

radios, televisions, mobile phones, cordless phones and in many other instruments. Other types of radiation include exposure to the magnetic field caused by being close to electrical equipment, earth's magnetic field, wiring in homes, and transmission lines. These are defined as extremely low frequency (ELF) waves.

#### 2.1.2 Ionizing radiation

Some forms of radiation are powerful enough to dislodge electrons from their atomic orbits, causing a shift in the electron/proton balance and a positive charge on the atom. Ions are the name for molecules and atoms that are electrically charged [3]. Ionizing radiation is the name for radiation that can create ions.

Ionizing radiation comes in many different forms, mostly as a result of charged particles, neutral particles, and photons. These are a few of the relevant ones:

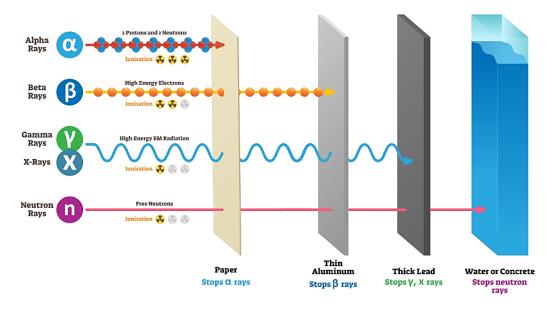

#### Alpha radiation:

Two protons and two neutrons make up alpha radiation; as they lack electrons, they have a positive charge. Alpha particles can scarcely penetrate skin due to their size and charge, and can be fully blocked by a piece of paper. [4].

#### Beta radiation:

Fast-moving electrons that have been expelled from an atom's nucleus make up beta radiation. Beta radiation is more invasive since it has a negative charge and is roughly 1/7000<sup>th</sup> the size of an alpha particle [4]. A modest amount of shielding, such as a sheet of plastic, can block beta radiation.

#### Gamma radiation:

Gamma radiation has a high penetration level. It often occurs soon after an atom's nucleus releases an alpha or beta particle. It may travel through the human body since it has no mass or charge, but denser things like concrete or lead absorb it [4].

#### X-rays:

While X-rays are a kind of radiation similar to gamma radiation, they are mostly created by artificial techniques as opposed to radioactive materials [4]. In contrast to light, X-rays have a higher energy and can penetrate most materials, including the human body. Images of inside organs and tissues are created using medical X-rays.

#### Neutron radiation:

When nuclear fission and other processes cause neutrons to be released from the nucleus, neutron radiation results. Nuclear fission is exemplified by the nuclear chain reaction, in which the release of a neutron from one fissioned atom triggers the fission of another, releasing more neutrons. Neutron radiation, unlike other types of radiation, is absorbed by substances like plastics and paraffin wax which contains a lot of hydrogen atoms. Figure 2.2 displays the various radiations' decay types.

Figure 2.2: Types of decay for various radiation [3].

People are regularly exposed to electromagnetic radiation in their daily lives thanks to devices like microwaves, mobile phones, and X-rays for medical diagnosis. There are various naturally occurring sources of electromagnetic and ionizing radiation in addition to technology made by humans, such as radio transmitters, light bulbs, heaters, and gamma-ray sterilizers (machines that destroy microorganisms in fresh or packaged food). These comprise stars, other astronomical phenomena like quasars or galactic centers, as well as radioactive substances in the Earth's crust and radiation trapped in the planet's magnetic field. [3].

The Sun is the principal radiation source for Earth. All electromagnetic spectrum wavelengths are emitted by the Sun. Visible, infrared, and ultraviolet radiation (UV) make up the bulk. On occasion, the Sun's surface experiences enormous explosions known as solar flares and coronal mass ejections (CME), which release enormous quantities of energy into space in the form of X-rays, gamma-rays, and streams of protons and electrons known as solar particle events (SPE).

Galactic Cosmic Radiation, or GCR, is a kind of radiation that originates largely from inside our Milky Way galaxy but also from sources beyond the solar system. GCR are massive, high-energy ions of elements that have had all of their electrons removed during their almost light-speed passage through the galaxy. They may ionize atoms as they move through matter and essentially unhindered through the skin of an astronaut or a normal spaceship. Current spacecraft and upcoming space missions must contend with the GCR, which is a prominent source of radiation in our solar system [3]. The average strength of these particles, which are influenced by the Sun's magnetic field, is highest during the minimal sunspot period when the Sun's magnetic field is least strong and least able to deflect them.

#### 2.2 Systems used for radiation measurement

A sensor or detector is a device or part of a system that monitors several factors, including physical, chemical, biological, and others [5]. Radiation is defined as the energy emitted by a source via a medium in the electromagnetic spectrum, ranging from radio waves with the smallest wavelength to gamma radiation with the largest energy.

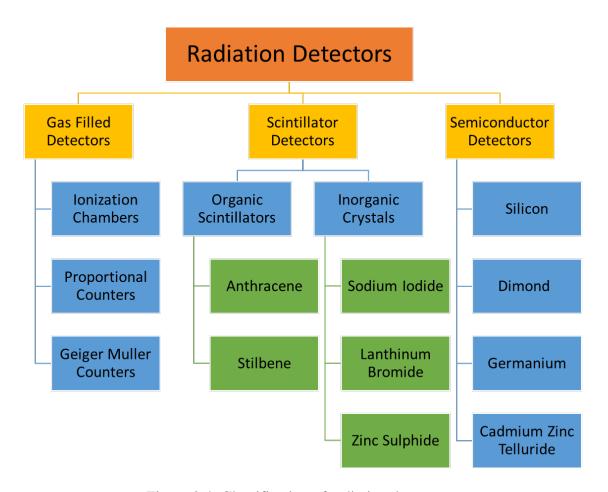

Radiation detectors operate on the principle of ionization to identify radiation particles such as alpha, beta, gamma, X-ray, protons, neutrons, etc. [6]. A highly energetic nuclear particle that enters a material medium ionizes the medium, which may be detected using various sensor techniques.

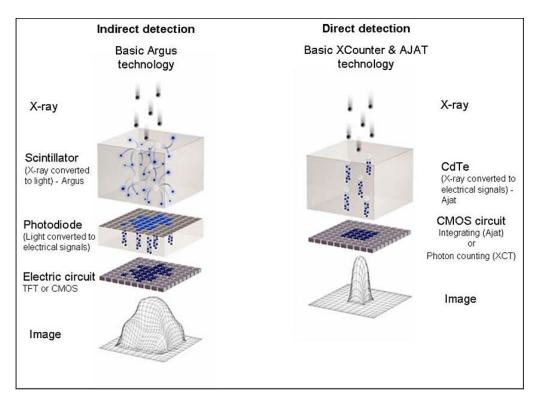

Direct or indirect methods are used to convert the photon energy emitted by the detector material during the encounter into an electrical signal; the conversion factor varies depending on the detector [7]. Consequently, radiation detectors may be generically divided into two categories.

- 1. Direct conversion type

- 2. Indirect conversion type

A direct conversion type detector is the one in which the incoming photon is directly converted into an electrical signal, whereas in an indirect conversion type detector, the conversion takes place in two steps. The first step involves conversion of photon into visible light and the second step involves the conversion of visible light into electrical pulse. The schematic representation of production of charge carriers in direct and indirect conversion type detector is shown in Figure 2.3.

Figure 2.3: Schematic representation of the production of charge carriers in direct and indirect conversion type X-ray detectors [8].

The indirect conversion approach induces loss of information in the process particularly at very low radiation inputs. Direct conversion detectors are those that directly convert input photon energy into a certain quantity of charge, which is subsequently collected at the output electrode of the device. These include semiconductor detectors and gas-filled detectors. Since there is no charge loss in the direct conversion type, it offers superior energy resolution. The energy required to create one electron-hole (e-h) pair in gas-filled detectors varies from 25 - 35 eV and in the case of a semiconductor detector, it is of the order of few eVs (for silicon, 3.6 eV and for germanium, 2.9 eV).

Scintillation detectors are indirect conversion types, wherein the incident radiation is converted into a shower of optical photons (visible and near visible region). Using photodetectors, these photons are subsequently captured and transformed into electrical charge. The photodetector may be a silicon photo detector, a photomultiplier tube (PMT), or a fairly recent technological innovation called a silicon photomultiplier (SiPM). Due to two-step conversion mechanism in the indirect conversion process, there is loss of signal due to light coupling, resulting in poor energy resolution. The average energy required to create one e-h pair in scintillators is of the order of 25 eV.

Biological, chemical, and physical parameters are measured by sensors, which play a key role in monitoring, measuring, and controlling systems [9]. Radiation is the energy that comes from a source and travels through a medium as waves or particles in the electromagnetic spectrum. Gamma radiation is the hottest and most potent type of radiation, whereas radio waves are the newest and have the shortest wavelengths.

Based on the ionization principle, a nuclear detector is a device that can identify several types of particles, including protons, neutrons, beta particles, gamma rays, X-rays, and alpha particles [10]. When a very energetic nuclear particle interacts with a material medium and ionizes it, radiation can be detected. Different types of sensors, broadly categorized in Figure 2.4, are needed to detect this energy.

Figure 2.4: Classification of radiation detectors.

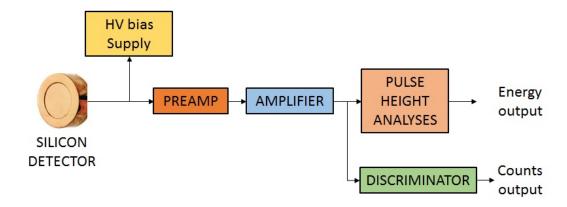

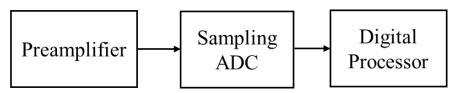

In order to correctly extract the energy or temporal information involved with radiation interactions, the majority of radiation detectors require pulse (or signal) processing circuitry. The general block diagram for the readout of the radiation detector is shown in Figure 2.5. The radiation detector generates the charge cloud, which will be converted into an electrical form by a pre-amplifier. The pre-amplifier signal will be

used in a subsequent step to calculate the incident energy. The voltage pulse produced from the pre-amplifier has an amplitude that is directly proportional to the incident energy. The pre-amplifier's output pulse generally has an amplitude of a few tens to hundreds of millivolts and is too small to directly measure. Consequently, the pulse is often processed through a linear amplifier as the following step where the voltage gain of ten or more can be given. The shaped linear pulse at this location will cover a range of 0 to 10V or ADC reference voltage. In a simple counting system, the shaping requirements are often not harsh; it is only when the counting rate is rather high that one needs pay great attention to the particular type of shaping chosen. The pulse height analyzer will receive the amplified signal from the shaping amplifier.

Figure 2.5: Radiation detector readout block schematic.

The process of determining the amplitude of the voltage or current pulse is called pulse height analysis. The shaped linear pulse must be transformed into a logic pulse in order to accurately count the pulse. The integral discriminator, which consists of a device that produces a logic output pulse only if the shaped input pulse amplitude exceeds a predetermined discriminating level, is the simplest way to detect the particle interaction. The process of pulse height analysis can be started using the logic pulse. There are multiple radiation detectors available which can be used to make instruments and derive various methods of PHA.

Sections 2.3, 2.4, and 2.5 of Chapter 2 will cover various types of detectors used in X-ray, Gamma-ray, and particle detection, with a focus on semiconductor detectors, specifically silicon detectors. A gamma-ray or X-ray detector is a transducer that converts photon energy into voltage pulses. The interaction of an X-ray photon within the active volume of the detector produces charge carriers (electron-hole pairs) through photoionization process. The current pulse produced by these charge carriers is

converted to a voltage pulse, by a charge to voltage conversion amplifier known as charge sensitive pre-amplifier. The incoming X-ray photon's energy is directly proportional to the voltage amplitude of the pulse. The signal is then processed by a suitable low-noise electronics chain to obtain the energy and other required parameters such as arrival time, the angle of arrival, position of interaction etc. X-ray detectors are also used to detect other types of electromagnetic radiations such as electrons, protons and alphas etc.

#### 2.3 Summary

The working principle and various types of radiation detectors are discussed in this chapter. This chapter also discusses technologies used in X-ray studies over the last several decades, including their operating principles, charge formation, and readout techniques. The suitability of these detectors for the desired energy range is described by comparing their performances and highlighting their advantages and disadvantages. Because of advancements in silicon detector technology, it is possible to design X-ray spectrometer instruments with energy resolution close to the Fano limit. The application of silicon detectors in various applications is also covered.

#### 3 EXPERIMENTAL METHODS

The various components required to develop radiation detection instruments like a detector, various types of CSPA, shaping amplifier, high voltage bias and pulse height analysis techniques are discussed in this chapter.

#### 3.1 Detector and Pre-amplifier

One of the crucial aspects of an experiment is the choice of an appropriate detector. The detector must be a radiation detector and be simple to operate in a lab setting without the need for special shielding or vacuum. In this opinion, the silicon drift detector (SDD) is a practical choice since it is frequently offered as modules with a built-in Peltier, which removes the need for liquid nitrogen (LN) cooling, and a temperature sensor for accurate temperature control [63]. The SDD detector supports throughput count rates of up to 100 Kcps and can tolerate significantly greater input count rates. The SDD provides better resolution in the 1–15 keV range.

#### 3.1.1 Silicon Drift Detector (SDD)

Silicon Drift Detector (SDD) is a new technology silicon photodetector with a unique electrode structure and offers low detector capacitance compared to planar Si PIN detector of the same area. This yields low noise even at shorter shaping times and hence, SDDs can be used at much higher count rates with desired energy resolution. The concept of SDD was introduced in 1984 by Gatti and Rehak, who presented the concept and the experimental results [64]. The concept was based on sideward depletion. SDD was initially proposed for position measurement and considered as a replacement for gas chambers in the form of a solid-state device. In his work, it was observed that detector capacitance is independent of detector area. In 1985, Rehak and Gatti [65] showed the use of SDDs for energy measurements rather than position measurement with SDD in circular form. In these SDDs, the drift electrodes are made on both sides to form the radial electric field. The planar electrode concept in SDD was introduced in 1987 by Kemmer [66] with planar contact on one side and drift electrodes on the opposite side. As discussed in the earlier chapter, the fabrications of planar

contacts are easier to manufacture. This technique also provides a very thin dead layer in the entrance window where only X-ray photons are allowed to enter into the detector, which is important for X-ray spectroscopy. The first good-quality SDD for laboratory application was produced in 1995 for EDS and XRF measurements [67]. In the last two decades, SDDs have been optimized to achieve very good spectral energy resolution in various types and sizes [68, 69, 70, 71]. Significant research work has been carried out on the SDD readout techniques [72, 73, 74], aiming at improving the energy resolution by reducing the contribution of electronics noise. In recent times, it has been shown that SDDs with advanced readout electronics can provide energy resolution close to the Fano limit.

#### 3.1.1.1 Working principle of SDD

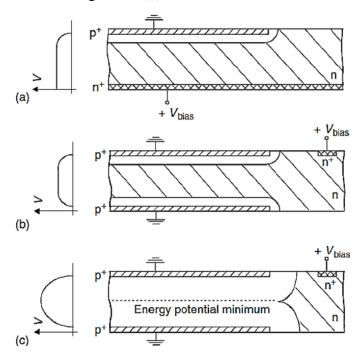

In the conventional PIN photodetector, the ohmic n+ contact extends to the full area of the silicon bulk on one side, and the potential distribution is shown in Figure 3.1 (a). In Figure 3.1 (b), n+ contact is introduced with p+ electrodes on both the sides to achieve the depletion of the bulk and when the bias at n+ contact is increased, creating a potential minimum at center of the bulk with a small undepleted zone near the n+ region as shown in Figure 3.1 (c).

Figure 3.1: Schematic representation of sideward depletion concept [64].

The working principle of the drift detector is understood from the sideward depletion concept. In the case of SDD, an additional electric potential is applied on both

sides to force the electrons to drift towards the n+ electrode for the signal readout, as shown in Figure 3.2.

Figure 3.2: Schematic representation of the working principle of silicon microstrip detector [64].

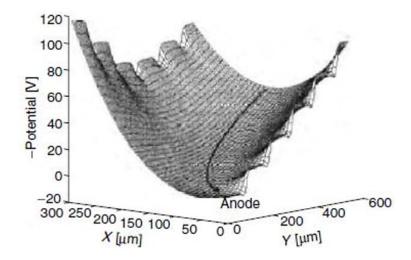

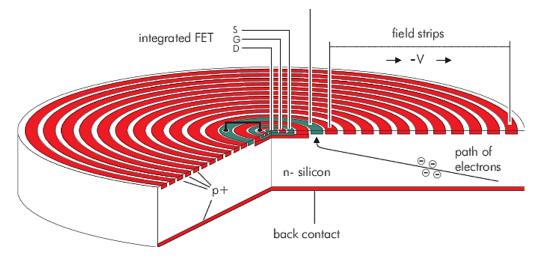

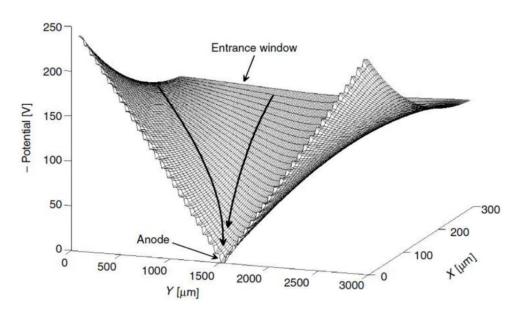

This is achieved by implanting the p+ electrode on both sides. These electrodes are suitably biased such that an electric field line is created, as shown in Figure 3.4. When a photon interacts in the active volume of the detector, the electrons are guided towards the anode and the holes are collected by the nearest p+ electrodes as the p+ electrodes are applied with negative bias. By appropriately biasing the opposing electrodes, the bottom of the potential channel is pushed away from the area near the collecting anode and towards the surface where the anode is located. The electron cloud gives an electric pulse in the anode and the drift time of the electron cloud along with the signal due to holes can be used to derive the measure of the position of the photon interaction [65].

Figure 3.3: The electron guiding potential distribution in the drift region of the SDD pointing towards the anode [64].

The signal due to electron charge will give the energy of the photon. The important finding of this sideward depletion concept is that the detector capacitance is the anode capacitance whose value is independent of the detector area. The anode capacitance is of the order of a few hundred femtofarad. The low detector capacitance provides low noise at shaping times near to  $1\mu s$ . Thereby the system can be used for high count rate applications.

#### 3.1.1.2 SDD for X-ray measurements

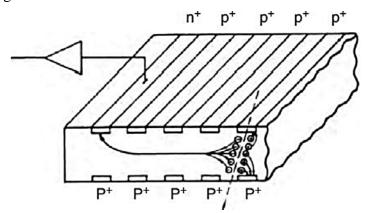

SDDs are ideally suited for X-ray spectrometry due to their low detector capacitance along with the low noise readout system enables them to achieve an energy resolution close to the Fano limit. In the sideward depletion SDD concept, the areas between the p+ strips on the surface are covered with SiO<sub>2</sub> layer. Since the SiO<sub>2</sub> layer contains fixed positive charges, potential minima are created by the spread of potential energy away from the detector surface. The signal electrons produced during photon interaction in the low energy range, <5 keV, might be collected at these locations. [75]. To overcome this limitation at lower X-ray energies, a suitable design topology has been implemented with a thin continuous entrance window without oxide layer gaps [76]. Also, the point anode is kept in the center forming a circular detector that minimizes any signal loss due to the travel length of the signal electrons. The circular SDD optimized for energy measurement is shown in Figure 3.4. Circular SDDs have concentric rings around the point anode, which are applied with progressively higher reverse bias voltages, which guide the photoelectrons into a "point" anode. The drift field with respect to the point anode at the center is shown in Figure 3.5.

Figure 3.4: Schematic representation of a circular SDD with anode at the center (courtesy: KETEK, GmbH) [77].

Figure 3.5: The possible electron path (field line) inside the SDD with 300-micron thickness [77].

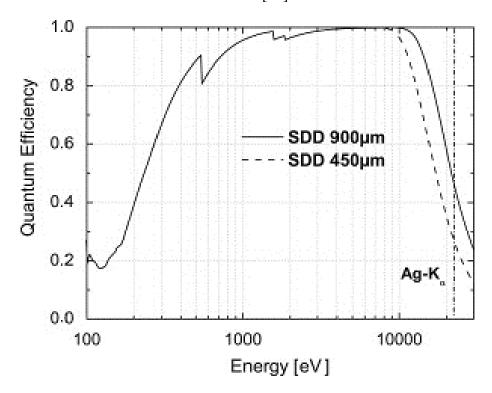

Figure 3.6: Quantum efficiency of 450 and 900-micron thick SDDs with thin dead layer [78].

The bias voltages required for the successive p+ electrodes are derived from a single high voltage applied at the outer electrode by using a resistive divider, which is part of the SDD chip. The inner ring close to the anode and the back contacts are applied with separate bias voltages. The capacitance of the point anode is ~200 fF. The p+ back

contact acts as an entrance window for the radiation to be detected and is made of a shallow p+ implantation with a thickness of the order of a few tens of nanometers [79] which allows to achieve the low energy threshold of a few hundred eV. The quantum efficiency of such SDD with few tens of nm of dead layer for 450 and 900-micron thick detector is reported in [78]. It is shown that quantum efficiency of > 40% could be achieved for incident energies of more than 200 eV as shown in Figure 3.6.

#### 3.1.1.3 SDDs in space missions

Due to its better spectroscopic performance, X-ray spectrometers based on Silicon Drift Detectors (SDD) have been flown on several space missions during the past ten years for a variety of scientific experiments. Earlier space investigations, such as the MinXSS experiment to measure the solar X-ray spectrum on a CubeSat [63], and the solar X-ray monitor (XSM) on the Chandrayaan-2 [80], The APXS instrument on Mars rovers Curiosity, Spirit, and Opportunity [81, 82], The PIXL instrument on mars rover Perseverance [83], and neutron star interior composition explorer (NICER) for soft X-ray timing and spectroscopy of astrophysical sources [84] employed silicon drift detectors. The comet mission Rosetta also carried SDD based X-ray spectrometer onboard PHILAE lander for the comet 67P/Churyumov-Gerasimenko to carry out insitu elemental composition measurements. Recent lunar mission from China, Change'3 also carried SDD for in-situ elemental composition measurements on the lunar surface.

There are planetary/space missions in the near future plan to use scientific instruments having SDD as a sensor. Chandrayaan-3, the Third Indian mission to Moon is slated for launch in the year 2023 uses SDD detector in one X-ray spectrometer instruments. The space mission, Large Observatory for X-ray Timing (LOFT) is being developed by European Space Agency (ESA) with large number of large area SDDs with total effective area of 10 m<sup>2</sup> for astronomical observations. This mission is slated for launch in the coming years.

#### 3.1.1.4 SDD detector module used for an experiment

The main advancement of SDD devices is the application of concentric rings in the detector region. These rings are used with increasingly higher bias voltages to direct the photo-electrons created to a point anode when an X-ray is absorbed. The anode's minimal surface area maintains an extremely low capacitance. This is significant

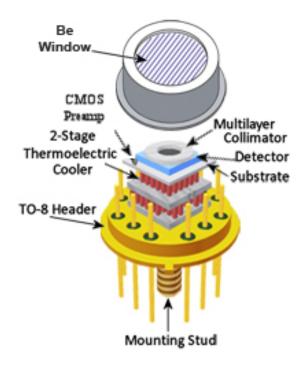

because total input capacitance, which is proportional to voltage noise, is the primary noise source in silicon X-ray spectroscopy. The SDD has less noise because to its low capacitance, especially during extremely fast shaping periods. The field-effect transistor (FET), which makes up the first stage of the charge-sensitive pre-amplifier (CSPA), and the feedback capacitor, which integrates charge from the detector anode, are both present in the silicon drift detector (SDD) module because they are essential to the SDD's performance [63]. Because of its space heritage and compatibility with the in-house built charge-sensitive pre-amplifier (CSPA), the silicon drift detector (SDD) module was purchased from KETEK for the experiment.

Figure 3.7: Silicon drift detector (SDD) module with lid, KETEK VITUS H80 (left). Views of the TEC and on-chip collimator from an unencapsulated silicon drift detector (SDD) module (right). [24] (Image courtesy of KETEK GmbH.)

Figure 3.8: SDD module schematic view [85] (courtesy: KETEK, GmbH - H80).

The KETEK SDD detector used in the experiment has the component number VITUS H80. The detector is housed in a typical TO-8 package and has a wide collimated area of  $80~\text{mm}^2$ , a diameter of 21~mm, a height of 19.5~mm. Figure 3.7~shows the KETEK SDD module in detail. The module has a  $25~\mu\text{m}$  thick filter window which is made up of Be (Beryllium) with DuraCoat and it is installed on the TO-8 package cap that is visible in a detector's explored view (Figure 3.8). This Be filter will restrict the ambient light to saturate the detector. The detector's chip has a thickness of  $450~\mu\text{m}$ . The silicon bulk of the SDD must be completely depleted by applying a negative voltage to the detector's back contact in order to make the sensor sensitive to incoming photons.

An NTC thermistor with a resistance of 10 k $\Omega$  at 25 °C is used to measure the temperature within the detector. To operate the detector at negative temperatures, a Peltier cooler is attached to it within a container. The inside schematic view of the detector made by KETEK is shown in Figure 3.9.

Figure 3.9: Internal electrical interconnection diagram of SDD module [86] (courtesy: KETEK, GmbH).

High voltage biases of -20 V, -130 V, and -60 V are supplied to the SDD's Inner Ring (R1), Outer Ring (RX), and Back Contact (RBACK) electrodes in order to

produce an electric field that directs electrons to the anode through the SDD detector. Similar to this, the drain, source, and bulk of a FET have corresponding bias voltages of  $3V \pm 0.5~V \ @ 3~mA$ , 0~V, and  $-5~V \pm 1~V$ . The maximum rating for the peltier element is 4.5~V and 1~A with a maximum differential temperature of  $75~^{\circ}C$ . Table 3.1 is a list of the SDD detector's specifications..

Table 3.1: Specifications of the SDD module planned for the experiment

| Sr. No. | Parameter                | Values/ Components                      |

|---------|--------------------------|-----------------------------------------|

| 1       | Area                     | 80 mm <sup>2</sup>                      |

| 2       | Absorption depth         | 450 μm                                  |

| 3       | Windows                  | 8 μm Be (with 1-micron thick Dura Coat) |

| 4       | Cooling performance      | ~T > 75 K                               |

| 5       | $HV(R_1, R_X, R_{BACK})$ | -20 V, -130 V and -60 V                 |

| 6       | Peltier Element          | 4.5 V, 1 A                              |

| 7       | Temperature monitor      | Thermistor, 10 KΩ at 20°C               |

# 3.1.1.5 Design of Charge Sensitive Pre-Amplifier (CSPA):

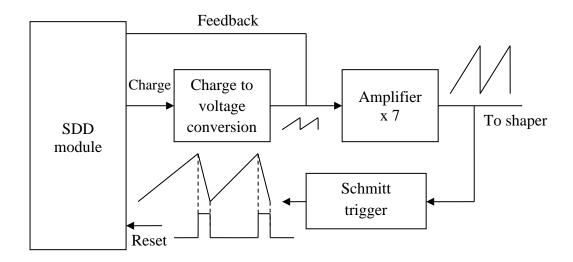

The block schematic of the developed charge-sensitive pre-amplifier along with SDD is shown in Figure 3.16. The first stage of the charge-sensitive pre-amplifier is the charge to voltage conversion amplifier, where the internal FET is operated in a common source configuration. The internal charge storing capacitor is connected to the feedback path that determines the gain of the charge to voltage conversion amplifier. The output of the charge to voltage conversion amplifier is connected to the gain amplifier to provide additional gain to the feeble signal that is of the order of < 1 mV/keV.

Figure 3.10: Block schematic of pulse reset type Charge Sensitive Pre-Amplifier (CSPA) design [105].

The feedback capacitor integrates the leakage current and also the current pulses due to photon interaction. The charge is integrated into the form of a ramp signal and the charge should be removed before the amplifier attains the saturation limits. To generate the reset pulses to remove the charge in the feedback capacitor, the output of the gain amplifier is fed to Schmitt trigger-based reset pulse generator, which gives reset pulses when the ramp signal amplitude crosses the set threshold limit. The duration of the reset pulse is set  $\sim 1~\mu s$  which is fed to the reset diode to discharge the charge stored in the feedback capacitor. The selected operational amplifier device for the CSPA design is AD829 which has a wide bandwidth of 28 MHz, low input noise of  $4~nV/\sqrt{Hz}$  and a high slew rate of 230 V/ $\mu s$ . The Schmitt trigger is made using comparator LM311.

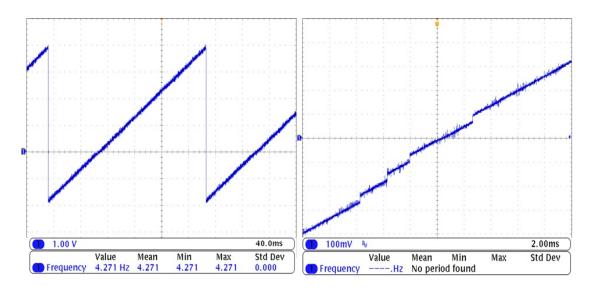

The amount of the leakage current produced by the SDD in the absence of any photons interacting with the detector will determine the ramp signal frequency at the CSPA's output. Figure 3.17 displays one such ramp signal that was recorded in the cathode ray oscilloscope (CRO) (left). The ramp signal frequency fluctuates with the energy and rate of a photon interacting with the detector when there are photon interactions present. Each photon interaction appears as a step voltage pulse on the ramp and the magnitude of the step pulse is proportional to the incident photon energy as shown in Figure 3.17 (right).

Figure 3.11: CRO screenshot for ramp signal output from CSPA (left), Step on the ramp signal indicating X-ray interaction with the SDD detector (right).

The amplitude of a step pulse at the output of charge to voltage conversion amplifier of CSPA (first stage of CSPA) is  $\sim 0.74$  mV/keV (assuming the value of  $C_f$  is  $\sim 60$  fF) and at the final output of CSPA is  $\sim 5$  mV/keV. Application Specific Integrated Circuit (ASIC) based charge readout ICs have been developed in recent times [99, 100, 101] and shown to provide the energy resolution of  $\sim 140$  eV at 5.9 keV for small area SDD modules. Recently, a CMOS-based ASIC has been developed [102] that is integrated along with the small area SDD module and has shown to provide an energy resolution of  $\sim 125$  eV at 5.9 keV.

The step pulses must be turned into a semi-gaussian pulse after being converted from charge to voltage, or they can be supplied directly to an FPGA or digital signal processor (DSP) for pulse processing after being digitized.

## 3.1.2 Shaping Amplifier

A shaping amplifier is generally used following the CSPA stage that performs three functions. First, the shaping amplifier provides an output pulse with a faster return to the baseline than the CSPA, which has a peak to baseline return time of a few tens of microseconds. This is crucial at high count rates because successive event pulses have a tendency to "pile up." Other than that, by narrowing the signal bandwidth as needed for the application, the shaping amplifier removes noise from the pre-amplifier output signal. Finally, the shaping amplifiers also provide the necessary gain to amplify the signal from CSPA, which is very small (few mV/keV). A shaping amplifier is a

combination of high pass and low pass filter amplifiers, which reduces the signal bandwidth and thereby improves the signal-to-noise ratio and provides the necessary gain to match the analog to digital converter (ADC) range. The output of the shaping amplifier will be in the form of a semi-gaussian pulse and one can get close to a gaussian pulse shape by increasing the number of low pass filter amplifiers in the design. The shaping amplifier is designed with three stage amplifier, first stage is the CR high pass filter amplifier which defines the desired fall time of the signal with the  $C_1R_1$  time constant. It is represented by the equation (3.9)

$$V_d = V_{in} e^{-\frac{t}{\tau_d}} \tag{3.1}$$

Where,  $V_d$  is the signal amplitude at the output of the  $C_1R_1$  differentiator and  $\tau_d$  is the differentiator time constant. The amplifier after the CR stage is known as CR amplifier, providing suitable gain to an output signal having a fast rise time. The output of the CR filter amplifier is given to two-stage RC low pass filter amplifiers with time constants of  $R_2C_2$  and  $R_3C_3$  respectively. The two-stage RC filter amplifier defines the rise time or peaking time of the pulse. The equation for a one-stage RC filter is given in equation (3.10).

$$V_i = V_d \left( 1 - e^{-\frac{t}{\tau_i}} \right) \tag{3.2}$$

Assuming the CR differentiator and RC integrator time constants are equal i.e.,  $\tau_{d} = \tau_{i} = \tau$ , then the equation becomes (3.11).

$$V_o = V_{in} \left(\frac{t}{\tau}\right) e^{-\frac{t}{\tau}} \tag{3.3}$$

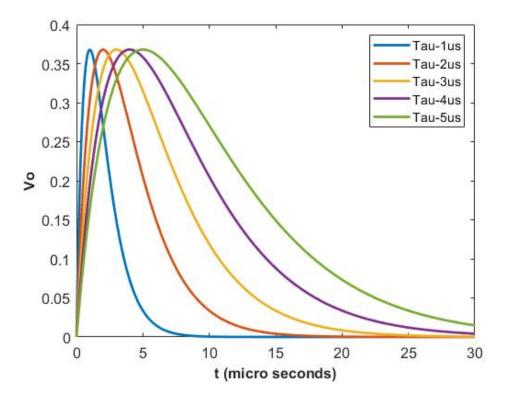

The output of the *CR-RC* type shaping amplifier with step input for  $\tau_d = \tau_i$  is shown in Figure 3.18.

To get the shaping amplifier output close to Gaussian, the number of RC stages has to be increased and the equation becomes (3.12).

$$V_o = V_{in} \left(\frac{t}{\tau}\right)^n e^{-\frac{t}{\tau}} \tag{3.4}$$

Where, n is the order of RC integrator stages and the shaping amplifier output for one stage CR filter and a number of RC filters is shown in Figure 3.19. The shaping amplifier has been designed using AD829 op-amp with three-stage CR-(RC) 2 type (5 poles) shaping.

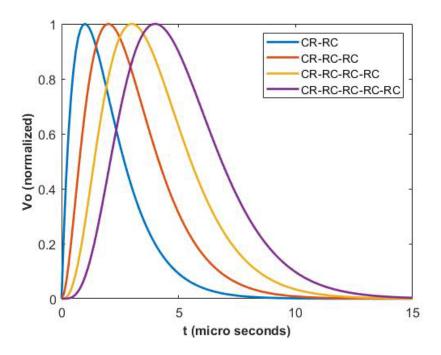

Figure 3.12: Simulated shaping amplifier output for equal CR-RC time constants.

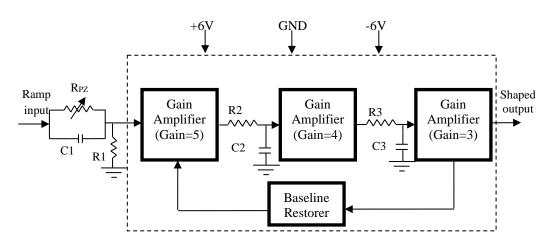

Increasing the number of RC stages will increase the hardware complexity substantially and hence limit to two-stage RC filters. The block schematic is shown in Figure 3.20. The shaping amplifier gain is decided based on the energy range covered by the spectrometer.

Figure 3.13: Simulated shaping amplifier output with one CR and multiple RC stages.

Figure 3.14: Block schematic of CR-(RC)<sup>2</sup> type shaping amplifier.

# 3.1.3 High Voltage Bias Generation for SDD

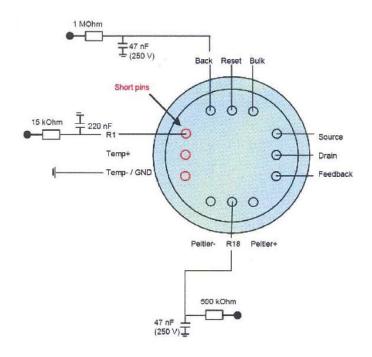

SDD requires three high voltages for its operation on the terminals namely outer ring R18 ( $R_x$ ), inner ring adjacent to anode  $R_1$  and back contact  $R_{BACK}$ . The schematic representation of the high voltage bias pin locations on the SDD module and the filter connections are shown in Figure 3.21.

Figure 3.15: Schematic representation of SDD with HV bias filtering requirement (courtesy: KETEK GmbH).

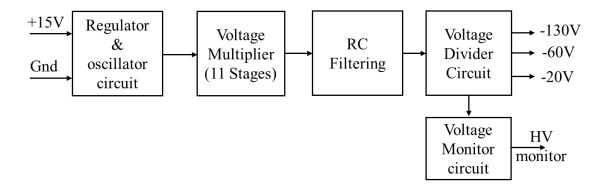

These high voltage biases are generated using a voltage multiplier-based circuit having eleven stages of voltage multiplication with the first stage being an RC oscillator with a frequency of about 100 kHz.

Figure 3.16: The block schematic of the high voltage generation circuit.

Each stage of the voltage multiplier uses a Schmitt trigger buffer with a diode capacitance combination for voltage multiplication. Hex Schmitt trigger inverter HC40106 IC is used for this purpose and the voltage multiplication is carried out with 15 V bias input. Three different voltages required for SDD operation are derived using a resistive voltage divider. The high voltage bias and the filtering requirement are listed in Table 3.2.

Table 3.2: SDD HV bias voltage, current and filtering on each HV line.

| SDD Ring                              | Typical voltage            | Filter requirement    |

|---------------------------------------|----------------------------|-----------------------|

| R1 Voltage, Current                   | -20V $\pm$ 1V, 10 $\mu$ A  | 15 kΩ, 220 nF         |

| R <sub>18</sub> (Rx) Voltage, Current | $-130V \pm 5V, 10 \ \mu A$ | 500 kΩ, 47 nF (250 V) |

| R <sub>BACK</sub> Voltage, Current    | -60V ± 2V, < 1 nA          | 1 MΩ, 47 nF (250 V)   |

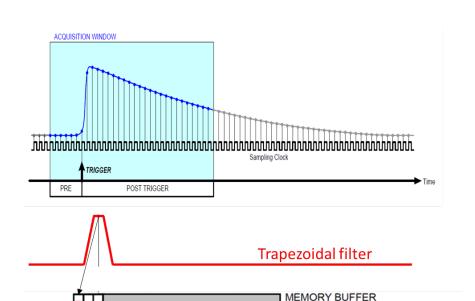

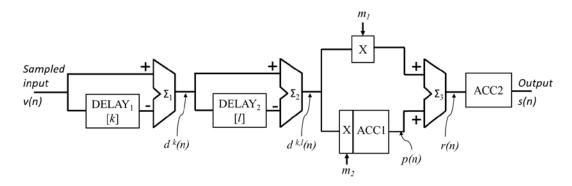

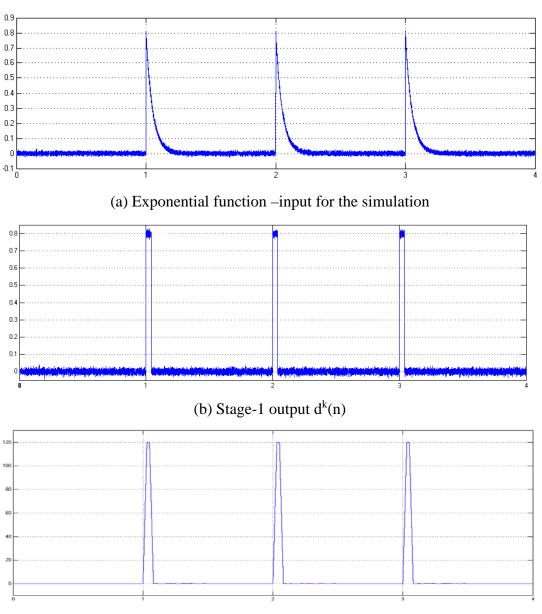

# 3.2 Pulse height measurement techniques

A Pulse-Height Analyzer (PHA) is a device that counts the pulses and measures their amplitude coming from a radiation detector. There are several methods for measuring pulse height. The peak hold detector-based approach, which keeps the peak of the semi-gaussian-shaped pulse form shaping amplifier output on hold until the ADC conversion time, is one of the conventional techniques. Digital pulse processing (DPP), a well-known method, samples the CSPA output using a high-speed ADC and processes it using an FPGA or DSP. The shaping amplifier output can be discharged linearly to measure the height of the pulse using the linear discharge technique (Amplitude of the Pulse is proportional to the discharge time). The pulse width modulation method, in which the pulse width is directly proportional to the input pulse amplitude, is also used to quantify pulse amplitude.

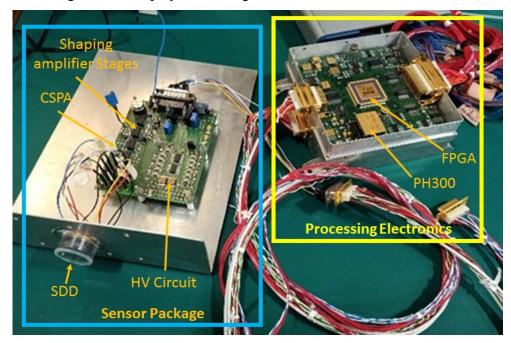

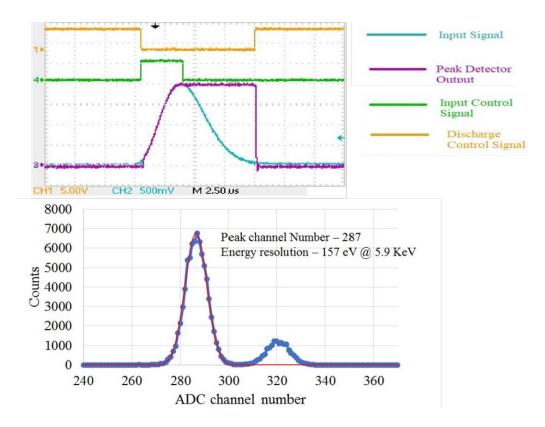

The identical front-end hardware, which comprises an SDD detector, CSPA, high voltage (HV) bias, and Peltier cooling circuit, is utilized to evaluate the performance of developed approaches. Using a Schmitt trigger-based multiplier circuit, the high voltages are produced. The thermistor value is monitored in order to keep the detector temperature at -35 °C at ambient temperature. Most of the time, the performance of the front-end component is unaffected by the back-end. For all the peak height measuring methods back-end hardware and FPGA algorithm is designed. In the next sections, all peak height measuring methods are thoroughly examined before being compared to the suggested approach. One of the primary factors used for technique comparison is spectral resolution. The spectra are measured by the full width at half maximum (FWHM) of the line at 5.9 keV and are obtained using a <sup>55</sup>Fe radioactive source available at lab.

## 3.2.1 The conventional peak detection technique

Usually, Soft X-ray spectrometer is designed in two parts front-end electronics and back-end electronics (processing electronics) package. The detector, CSPA, shaping amplifier, controller for the Peltier cooler, and high voltage supply to bias the detector make up the front-end electronics package. Back-end electronics will contain the semi-gaussian peak detection method and other processing.

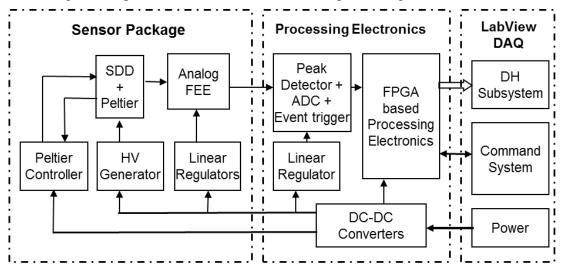

Figure 3.17: Block diagram of the peak detector-based spectrometer's front-end and back-end circuits.

The step pulse will be transformed into a semi-gaussian pulse with a 5µs peaking period by the CR-RC-RC filter. Figure 3.24 displays the spectrometer's block diagram. The peak detection, analogue to digital conversion, and further event processing are all started by the event trigger generator when an X-ray interacts with the detector.

#### 3.2.1.1 Peak hold detector

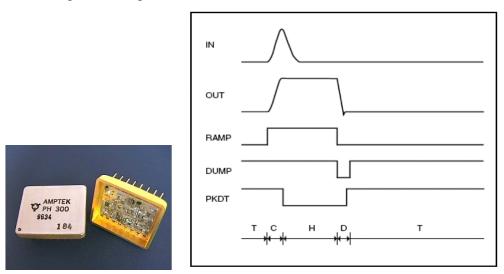

A peak detector circuit receives the output of the shaping amplifier and holds the peak amplitude value of the pulses until the analogue to digital process time. The design makes use of the hybrid peak detector PH300 module manufactured from AMPTEK. This is a hybrid module that is directly interfaced with the FPGA to initiate the peak detection and hold the peak value until the A/D conversion. Peak detector PH300 is having the following features

- 1. Low droop rate (10 n V/ms)

- 2. High speed (250 ns rise time)

- 3. Low power consumption (36 mW)

- 4. Fast discharge